## **DP5 Programmer's Guide**

## Amptek Inc.

14 Deangelo Drive, Bedford, MA 01730 PH: +1 781 275 2242 FAX: +1 781 275 3470 sales@amptek.com www.amptek.com

Note: This document applies to the Amptek DP5, PX5, TB5, DP5G, MCA8000D and products derived from these (X123, Gamma-Rad5).

## **Table of Contents**

| 1 | Cnai  | nge List                                  |     |

|---|-------|-------------------------------------------|-----|

|   | 1.1   | Programmer's Guide Rev B0 (this document) |     |

|   | 1.2   | Programmer's Guide Rev A8                 |     |

|   | 1.3   | Programmer's Guide Rev A7                 | 6   |

|   | 1.4   | Programmer's Guide Rev A6                 | 6   |

|   | 1.5   | Programmer's Guide Rev A5                 | 6   |

|   | 1.6   | Programmer's Guide Rev A4                 | . 7 |

|   | 1.7   | FW6.09.02/FP6.13                          | . 7 |

|   | 1.8   | FW6.09.01/FP6.13                          | . 7 |

|   | 1.9   | FW6.09.00/FP6.12                          | . 7 |

|   | 1.10  | FW6.08.06/FP6.11                          |     |

|   | 1.11  | FW6.08.04/FP6.10                          |     |

|   | 1.12  | FW6.08.03/FP6.09                          | 8   |

|   | 1.13  | FW6.08.02/FP6.07                          | 8   |

|   | 1.14  | FW6.08.01/FP6.06                          |     |

|   | 1.15  | FW6.08.00/FP6.06                          |     |

|   | 1.16  | FW6.07.05/FP6.04                          |     |

|   | 1.17  | FW6.07.04/FP6.03                          |     |

|   | 1.18  | FW6.07.02/FP6.01                          |     |

|   | 1.19  | FW6.06.07/FP6.01                          |     |

|   | 1.20  | FW6.06.06 / FP6.00                        |     |

|   | 1.21  | FW6.06.05 / FP5.13                        |     |

|   | 1.22  | FW6.06.04                                 | 10  |

|   | 1.23  | FW6.06.03                                 |     |

|   | 1.24  | FW6.06.02                                 |     |

|   | 1.25  | FW6.06.01                                 |     |

|   | 1.26  | FW6.06.00 / FP5.11                        |     |

|   | 1.27  | FW6.05 / FP5.10                           |     |

|   | 1.28  | FW6.04 / FP5.10                           |     |

|   | 1.29  | FW6.03 / FP5.10                           |     |

|   |       | FW6.02 / FP5.09                           |     |

| 2 |       | ware1                                     |     |

|   | 2.1   | Uploading new firmware                    |     |

|   | 2.2   | Software Resources                        |     |

|   | 2.2.1 | DP5 VB Demo                               | 12  |

|   | 2.2.2   | SDK                                                                         | 12 |

|---|---------|-----------------------------------------------------------------------------|----|

| 3 | Interfa | ces                                                                         | 12 |

|   | 3.1 U   | SB                                                                          | 13 |

|   | 3.1.1   | Installing the WinUSB Driver                                                | 13 |

|   | 3.1.2   | WinUSB GUIDs                                                                | 13 |

|   | 3.2 Et  | thernet                                                                     | 14 |

|   | 3.2.1   | Ping                                                                        | 14 |

|   | 3.2.2   | Ethernet Ports                                                              | 14 |

|   | 3.2.3   | General UDP Port                                                            | 14 |

|   | 3.2.4   | Netfinder UDP port 3040                                                     | 15 |

|   |         | S232                                                                        |    |

|   | 3.4 Ti  | ransfer times and data buffering deadtime                                   | 18 |

| 4 |         | Format                                                                      |    |

|   | 4.1 R   | equest Packets (Host PC to DP5)                                             | 21 |

|   | 4.1.1   | Request packet: "Request Status Packet"                                     | 24 |

|   | 4.1.2   | Spectrum Request Packets                                                    |    |

|   | 4.1.3   | Request packet: "Buffer spectrum"                                           | 26 |

|   | 4.1.4   | Request packet: "Buffer & clear spectrum"                                   | 26 |

|   | 4.1.5   | Request packet: "Request buffer"                                            | 27 |

|   | 4.1.6   | Request packet: "Request Digital Scope Data"                                |    |

|   | 4.1.7   | Request packet: "Request Digital Scope Data & Re-arm Scope"                 | 28 |

|   | 4.1.8   | Request packet: "Request Misc Data"                                         |    |

|   | 4.1.9   | Request packet: "Request Ethernet Settings"                                 |    |

|   | 4.1.10  | Request packet: "Request Diagnostic Data"                                   | 31 |

|   | 4.1.11  | Request packet: "Request Netfinder Packet"                                  |    |

|   | 4.1.12  | Request packet: "I <sup>2</sup> C Transfer"                                 |    |

|   | 4.1.13  | Request packet: "Request List-Mode Data"                                    |    |

|   | 4.1.14  | Request packet: "Request Option PA calibration data" [MCA8000D only]        |    |

|   | 4.1.15  | Request packet: "Request 32-bit SCA Counters"                               |    |

|   | 4.1.16  | Request packet: "Latch + Request 32-bit SCA Counters"                       | 36 |

|   | 4.1.17  | Request packet: "Latch + Clear + Request 32-bit SCA Counters"               |    |

|   | 4.1.18  | Request packet: "Text Configuration"                                        |    |

|   | 4.1.19  | Request packet: "Text Configuration Readback"                               |    |

|   | 4.1.20  | Request packet: "Text Configuration (without saving to nonvolatile memory)" |    |

|   | 4.1.21  | Request packet: "Clear Spectrum"                                            |    |

|   | 4.1.22  | Request packet: "Enable MCA/MCS"                                            |    |

|   | 4.1.23  | Request packet: "Disable MCA/MCS"                                           |    |

|   | 4.1.24  | Request packet: "Arm Digital Scope"                                         |    |

|   | 4.1.25  | Request packet: "Autoset Input Offset"                                      |    |

|   | 4.1.26  | Request packet: "Autoset Fast Threshold"                                    |    |

|   | 4.1.27  | Request packet: "Write IO3-0"                                               | 46 |

|   | 4.1.28  | Request packet: "Write 512-byte Misc Data"                                  |    |

|   | 4.1.29  | Request packet: "Set DCAL"                                                  |    |

|   | 4.1.30  | Request packet: "Set PZ Correction"                                         |    |

|   | 4.1.31  | Request packet: "Set uC Temperature Calibration"                            |    |

|   | 4.1.32  | Request packet: "Set ADC Calibration"                                       |    |

|   | 4.1.33  | Request packet: "Clear G.P. Counter"                                        |    |

|   | 4.1.34  | Request packet: "Set Ethernet Settings"                                     | 53 |

|   |         |                                                                             |    |

| 4.1. | 35 Request packet: "Select High-Pass Time Constant"       | 54 |

|------|-----------------------------------------------------------|----|

| 4.1. | 36 Request packet: "Select RS232 Baud Rate"               | 55 |

| 4.1. | 1 1                                                       |    |

| 4.1. |                                                           |    |

| 4.1. | 39 Request packet: "Clear/Sync List-mode timer"           | 58 |

| 4.1. | 40 Request packet: "Restart Sequential Buffering"         | 59 |

| 4.1. | $\iota$ $\iota$ $\iota$                                   |    |

| 4.1. | 42 Request packet: "Interface Keep-alive – Allow Sharing" | 61 |

| 4.1. | 43 Request packet: "Interface Keep-alive – No Sharing"    | 62 |

| 4.1. | 1 1 1                                                     |    |

| 4.1. | 1 1 1                                                     |    |

| 4.1. | 46 Request packet: "Comm test – Streaming test mode"      | 65 |

| 4.1. | 47 Request packet: "Comm test - Echo packet"              | 66 |

| 4.2  |                                                           | 67 |

| 4.2. | 1 Response packet: "Status Packet"                        | 68 |

| 4.2. | 2 Response packet: "256-channel spectrum"                 | 72 |

| 4.2. |                                                           | 72 |

| 4.2. | 4 Response packet: "512-channel spectrum"                 | 72 |

| 4.2. | 5 Response packet: "512-channel spectrum plus Status"     | 72 |

| 4.2. | 6 Response packet: "1024-channel spectrum"                | 72 |

| 4.2. | 7 Response packet: "1024-channel spectrum plus Status"    | 72 |

| 4.2. | 8 Response packet: "2048-channel spectrum"                | 72 |

| 4.2. | 9 Response packet: "2048-channel spectrum plus Status"    | 73 |

| 4.2. | 10 Response packet: "4096-channel spectrum"               | 73 |

| 4.2. |                                                           |    |

| 4.2. |                                                           |    |

| 4.2. | Response packet: "8192-channel spectrum plus Status"      | 73 |

| 4.2. |                                                           |    |

| 4.2. |                                                           |    |

| 4.2. | 1 1 1                                                     |    |

| 4.2. |                                                           |    |

| 4.2. | · · · ·                                                   |    |

| 4.2. |                                                           |    |

| 4.2. | i i                                                       |    |

| 4.2. | <u> </u>                                                  |    |

| 4.2. | 1 1                                                       |    |

| 4.2. |                                                           |    |

| 4.2. |                                                           |    |

| 4.2. | i i i                                                     |    |

| 4.3  | Acknowledge Packets                                       |    |

| 4.3. |                                                           |    |

| 4.3. |                                                           |    |

| 4.3. |                                                           |    |

| 4.3. |                                                           | 92 |

| 4.3. |                                                           | 92 |

| 4.3. |                                                           |    |

| 4.3. |                                                           |    |

| 4.3. | <b>5</b> 1                                                |    |

|      |                                                           |    |

## DP5 Programmer's Guide Rev B0

|   | 4.3.9            | Acknowledge packet: "PC5 Not Present"                                    | 93  |

|---|------------------|--------------------------------------------------------------------------|-----|

|   | 4.3.10           | Acknowledge packet: "Bad Hex Record"                                     | 93  |

|   | 4.3.11           | Acknowledge packet: "FPGA Error"                                         | 93  |

|   | 4.3.12           | Acknowledge packet: "CP2201 Not Found"                                   | 94  |

|   | 4.3.13           | Acknowledge packet: "Scope Data Not Available"                           |     |

|   | 4.3.14           | Acknowledge packet: "I <sup>2</sup> C Error"                             |     |

|   | 4.3.15           | Acknowledge packet: "Feature not supported by this FPGA version"         | 94  |

|   | 4.3.16           | Acknowledge packet: "Calibration data not present"                       | 94  |

| 5 |                  | Commands                                                                 |     |

|   | 5.1 T            | able 4 – ASCII Command Summary                                           |     |

|   | 5.1.1            | AINP - Set the Input Polarity                                            |     |

|   | 5.1.2            | AU34 - Select AUX3/4 Mode [PX5 only]                                     |     |

|   | 5.1.3            | AUO1 - Select AUX_OUT1 Signal                                            |     |

|   | 5.1.4            | AUO2 - Select AUX_OUT2 Signal                                            |     |

|   | 5.1.5            | BLRD - Select the Baseline Restorer 'Down' Correction                    |     |

|   | 5.1.6            | BLRM - Select the Baseline Restorer Mode                                 |     |

|   | 5.1.7            | BLRU - Select the Baseline Restorer 'Up' Correction                      |     |

|   | 5.1.8            | BOOT - Set Power-on State                                                |     |

|   | 5.1.9            | CON1 – Select signal for AUX1 Connector                                  |     |

|   | 5.1.10           | CON2 – Select signal for AUX2 Connector                                  |     |

|   | 5.1.11           | CLCK - Select FPGA Clock                                                 |     |

|   | 5.1.12           | CLKL - Select List-Mode Clock                                            |     |

|   | 5.1.13           | CUSP - Specify Non-Trapezoidal Shaping                                   |     |

|   | 5.1.14           | DACF - Set DAC Offset                                                    |     |

|   | 5.1.15           | DACO - Select Signal for Output DAC                                      |     |

|   | 5.1.16           | GAIA - Set the Analog Gain Index                                         |     |

|   | 5.1.17           | GAIF - Set the Fine Gain                                                 |     |

|   | 5.1.18           | GATE G. G. G. G. G. G. T. L. GATE I.                                     |     |

|   | 5.1.19           | GATE - Configure the GATE Input                                          |     |

|   | 5.1.20           | GPED - Select General Purpose Counter Edge                               |     |

|   | 5.1.21           | GPGA - General Purpose Counter Uses GATE                                 |     |

|   | 5.1.22           | GPIN - Select the Source for the General Purpose Counter                 |     |

|   | 5.1.23           | GPMC - General Purpose Counter is Cleared with MCA                       |     |

|   | 5.1.24           | GPME - General Purpose Counter Uses MCA Enable                           |     |

|   | 5.1.25           | HVSE - Turn On/Off the PX5/PC5 High Voltage Supply                       |     |

|   | 5.1.26<br>5.1.27 | INOG - Set the Input Offset Coin                                         |     |

|   | 5.1.27           | INOG - Set the Input Offset Gain                                         |     |

|   | 5.1.29           | MCAC - Select Number of MCA Channels                                     |     |

|   | 5.1.29           | MCAE - Select Number of MCA Chamlers  MCAE - Initial State of MCA Enable |     |

|   | 5.1.31           | MCAS - Select the MCA Source                                             |     |

|   | 5.1.31           | MCSL - Set Low Threshold for MCS                                         |     |

|   | 5.1.32           | MCSL - Set Low Threshold for MCS                                         |     |

|   | 5.1.34           | MCST - Set High Threshold for MCS  MCST - Set the MCS Timebase           |     |

|   | 5.1.34           | PAPS - Turn On/Off the Preamp Power Supplies                             |     |

|   | 5.1.36           | PAPZ – Preamp Pole-Zero Cancellation                                     |     |

|   | 5.1.37           | PAPZ – Preamp Pole-Zero Cancellation                                     |     |

|   | 5.1.38           | PDMD - Select the Peak Detect Mode [DP5, PX5, DP5G]                      |     |

|   | 2.1.20           | 12.12 Select the 1 can Detect 11000 [D1 0, 1 110, D1 00]                 | 130 |

| 5.1.39 | PDMD - Select the Peak Detect Mode [MCA8000D]                             | 139 |

|--------|---------------------------------------------------------------------------|-----|

| 5.1.40 |                                                                           |     |

| 5.1.41 |                                                                           |     |

| 5.1.42 |                                                                           |     |

| 5.1.43 | PREL - Preset Livetime [MCA8000D only]                                    | 143 |

| 5.1.44 |                                                                           |     |

| 5.1.45 | PRET - Preset Acquisition Time                                            | 145 |

| 5.1.46 | PURE - Pile-up Reject Enable [DP5, PX5, DP5G, TB-5]                       | 146 |

| 5.1.47 | <u>.                                     </u>                             |     |

| 5.1.48 | RESC - Reset the Configuration to Defaults                                | 148 |

| 5.1.49 | RESL - Select Reset Lockout Interval                                      | 149 |

| 5.1.50 | RTDD - Set Custom RTD Oneshot Delay                                       | 150 |

| 5.1.51 | RTDE - Enable Risetime Discrimination                                     | 151 |

| 5.1.52 | RTDS - Set Risetime Discrimination Sensitivity                            | 152 |

| 5.1.53 | RTDT - Set Risetime Discrimination Threshold                              | 153 |

| 5.1.54 | RTDW - Set Custom RTD Oneshot Width                                       | 154 |

| 5.1.55 | SCAH - Set SCA High Threshold                                             | 155 |

| 5.1.56 | SCAI - Set SCA Index                                                      | 156 |

| 5.1.57 |                                                                           |     |

| 5.1.58 | SCAO - Select SCA Output Level                                            | 158 |

| 5.1.59 | SCAW - Select SCA Output Pulse Width                                      | 159 |

| 5.1.60 | SCOE - Set Digital Scope Trigger Edge                                     | 160 |

| 5.1.61 |                                                                           |     |

| 5.1.62 | SCOT - Set Digital Scope Trigger Position                                 | 162 |

| 5.1.63 |                                                                           |     |

| 5.1.64 | SOFF - Set Spectrum Offset                                                | 164 |

| 5.1.65 | SYNC – Select List-Mode Sync Source                                       | 165 |

| 5.1.66 | TECS - Turn On/Off the PC5 Thermoelectric Cooler (TEC) Supply and Set the |     |

| Tempe  | erature                                                                   |     |

| 5.1.67 | 1                                                                         |     |

| 5.1.68 |                                                                           |     |

| 5.1.69 | 1                                                                         |     |

| 5.1.70 | TLLD - Select Threshold for Low-Level Discriminator (LLD)                 | 170 |

| 5.1.71 | $\boldsymbol{\mathcal{C}}$                                                |     |

| 5.1.72 |                                                                           |     |

| 5.1.73 |                                                                           |     |

| 5.1.74 | 1                                                                         |     |

|        | Topics                                                                    |     |

|        | ist-mode operation                                                        |     |

|        | treaming-mode operation                                                   |     |

|        | equential buffer operation                                                |     |

| 6.3.1  | Software-controlled Sequential Buffer Operation                           |     |

| 6.3.2  | Hardware-controlled Sequential Buffer Operation                           | 179 |

## 1 Change List

6

DP5 Programmer's Guide B0 is released with firmware version FW6.09.02, FPGA version FP6.13, and Visual Basic Demo v2.87.

Amptek Inc.

#### 1.1 Programmer's Guide Rev B0 (this document)

Current as of FW6.09.02/FP6.13

Support for DP5 Rev D

Significant enhancements to 16-bit List Mode (see section 4.2.22)

Cleaned up section 2, on uploading firmware

The sense of GATE for MCA8000D was reversed in section 5.1.19 – documentation was fixed, and a note was added mentioning how to change the sense, if that should be desired

Corrected MCA Source description for MCAS command (see section 5.1.31)

Added notes under PAPZ (for HPGe) and RESL relating to using RESL to reject overrange events (see sections 5.1.37 and 5.1.49)

#### 1.2 Programmer's Guide Rev A8

Current as of FW6.08.04/FP6.10

Fixed typo in section 4.2.19 – had incorrect PIDs for 'Text Configuration Readback' request packet

The 'Status packet' response packet has a few additions (section 4.2.1)

## 1.3 Programmer's Guide Rev A7

Current as of FW6.08.00/FP6.06 (see change list below)

MCA8000D documentation added

Equation for 'DP5 board temp (raw)' in diagnostic packet (Section 4.2.18) was in error. Fixed.

Added note to Text Configuration packet about delay caused by FLASH write

Section 6.3 is new (Sequential Buffering)

A note was added to Section 3 describing that in the DP5G, Ethernet is disabled at boot in the presence of USB or RS232

Section 3.1.2 was added, listing WinUSB GUIDs

Section 4.1 includes new Request Packets

The 'Status packet' response packet has a few additions (section 4.2.1)

New "Text Configuration (without saving to nonvolatile memory)" command was Request Packet was added (Section 4.1.20)

#### 1.4 Programmer's Guide Rev A6

Current as of FW6.06.06/FP6.00

#### 1.5 Programmer's Guide Rev A5

Section 6 is new.

Amptek Inc. Page 6 of 180

Describes FW releases

Current as of FW6.06.05/FW5.13

Section 3.1.1 mentions that the WinUSB driver is now available via Windows Update.

Section 3.1.2 adds a discussion of DHCP, and how to set a fixed IP address.

Documentation for List-mode operation (see sections 4.1.13, 4.1.20, 4.1.39, 4.2.22, 4.3.15, 5.1.12, 5.1.65, and 6.1)

#### 1.6 Programmer's Guide Rev A4

Added transfer times (section 3.4)

New commands and packet types are listed below, and in their corresponding sections

Current as of FW6.06.00/FW5.11

## 1.7 FW6.09.02/FP6.13

IF UPGRADING FROM FW6.07.04 OR EARLIER, FW7.00.01 MUST BE LOADED PRIOR TO UPGRADING TO THIS VERSION!!!

This version (or later) is required if upgrading a DP5 Rev D from FW5 to FW6

#### 1.8 FW6.09.01/FP6.13

IF UPGRADING FROM FW6.07.04 OR EARLIER, FW7.00.01 MUST BE LOADED PRIOR TO UPGRADING TO THIS VERSION!!!

Bug fix: Fast threshold defaulted to full-scale at power-up, if Auto fast threshold was used without subsequently commanding a fixed fast threshold. Fixed – now reverts to last commanded fast threshold.

#### 1.9 FW6.09.00/FP6.12

IF UPGRADING FROM FW6.07.04 OR EARLIER, FW7.00.01 MUST BE LOADED PRIOR TO UPGRADING TO THIS VERSION!!!

Support for DP5 Rev D – must use this version or later; different GAIA settings, ECO byte in status packet

DMCA: [with FP1.08] ECO=1 inverts the sense of the GATE signal; it was discovered this documentation specifies the opposite from how the MCA8000D actually performs.

DP5G/TB-5 support for CLYC scintillator [ECO=2]

Amptek Inc. Page 7 of 180

#### 1.10 FW6.08.06/FP6.11

## IF UPGRADING FROM FW6.07.04 OR EARLIER, FW7.00.01 MUST BE LOADED PRIOR TO UPGRADING TO THIS VERSION!!!

RTDS range doubled to 3187%

DMCA: Improved performance with bipolar pulses [with FP1.08]

THSL setting of 0 no longer allowed; defaults to 0.012% (1 ch out of 8192)

PX5: Allow RESL in conjunction with PAPZ to lockout processing after overrange events, which can cause spectrum artifacts. (In this context, RESL logic detects overrange events rather than resets.)

Additional support for deadtime correction in 16-bit List Mode (see section 4.2.22)

#### 1.11 FW6.08.04/FP6.10

## IF UPGRADING FROM FW6.07.04 OR EARLIER, FW7.00.01 MUST BE LOADED PRIOR TO UPGRADING TO THIS VERSION!!!

Fixed rounding error with HPGe PAPZ command readback (which was introduced in FW6.07.05)

Fixed SYNC command readback

New AU34 command

Fixed 0.1% timebase error in 16-bit List Mode

#### 1.12 FW6.08.03/FP6.09

## IF UPGRADING FROM FW6.07.04 OR EARLIER, FW7.00.01 MUST BE LOADED PRIOR TO UPGRADING TO THIS VERSION!!!

RTD timing improved for faster TPFA settings introduced in FW6.07.05/FP6.04

DPG/TB5: RESL can be used for gamma-ray rejection starting in FP6.09

#### 1.13 FW6.08.02/FP6.07

## IF UPGRADING FROM FW6.07.04 OR EARLIER, FW7.00.00 MUST BE LOADED PRIOR TO UPGRADING TO THIS VERSION!!!

LMMO command added for list mode, to improve ability to calculate deadtime (see sections 4.2.22, 5.1.28 and 6.1)

Streaming bug fix: streaming amplitude was a bit off at peaking times of 1.6uS or faster (at 80MHz)

#### 1.14 FW6.08.01/FP6.06

# IF UPGRADING FROM FW6.07.04 OR EARLIER, FW7.00.00 MUST BE LOADED PRIOR TO UPGRADING TO THIS VERSION!!!

Support for new product 'TB-5 Digital Tube Base'

Amptek Inc. Page 8 of 180

'SCTC' new command for DP5G and TB5

FP6.06 fast channel improved to reduce spurious fast-channel counts for DP5G and TB-5

#### 1.15 FW6.08.00/FP6.06

# IF UPGRADING FROM FW6.07.04 OR EARLIER, FW7.00.00 MUST BE LOADED PRIOR TO UPGRADING TO THIS VERSION!!!

Fixed bug in MCA8000D MCS timebase

Improved BLR initialization during reconfiguration

New Text Configuration Request Packet which skips the Flash write (Section 4.1.20)

New sequential buffering feature (Section 6.3)

#### 1.16 FW6.07.05/FP6.04

# IF UPGRADING FROM FW6.07.04 OR EARLIER, FW7.00.00 MUST BE LOADED PRIOR TO UPGRADING TO THIS VERSION!!!

More 'TPFA' (fast channel peaking time) options: 50, 100, 200, 400 or 800nS (80MHz); 200, 400, 800, 1600 or 3200nS (20MHz)

Default MCS Timebase ('MCST') changed to 1S; was 0, which is invalid

'Comm test – Streaming Test Mode' request packet added (Section 4.1.46)

'RESPER' (detector reset period) option added to 'GPIN' command

#### 1.17 FW6.07.04/FP6.03

'RESL' (Reset Lockout) can now be set with 1uS precision, rather than rounding to a power-of-2.

PX5-HPGe: HV is always turned off at power-up

Windows 8 USB descriptors were added, which may utilize WinUSB without having to install a USB driver (See section 3.1 – it is presently unclear if these actually work as Microsoft advertises.)

#### 1.18 FW6.07.02/FP6.01

'RTDS' command default changed from 0 to 2 (0 was an invalid setting)

GATE bit was in incorrect bit in status packet – fixed

'Option PA' calibration request packet, response packet and ACK packet for MCA8000D

#### 1.19 FW6.06.07/FP6.01

GATE state added to status packet

Additional PX5 HPGe support added

Amptek Inc. Page 9 of 180

#### 1.20 FW6.06.06 / FP6.00

'Streaming' feature added; 'STREAM' option added for 'AUO2' command (See section 6.2)

Additional fine-gain precision added

Increased ping data buffer size from 32 to 56 bytes, to handle default Linux ping size

DP5G: added support for Gammarad AD592 temperature sensor via PCG ADC; scintillator temperature shows up as 'detector temperature' in Status Packet

Added 16-bit List-mode capability ('SYNC=NOTIMETAG') (See sections 4.2.22, 5.1.65 and 6.1)

Added List-mode configuration byte in Status Packet (Section 4.2.1)

#### 1.21 FW6.06.05 / FP5.13

Default static IP address changed from 255.255.255.255 to 192.168.1.10

PX5: Power button changed from Green/Amber (+HV) or Red/Amber (-HV) to Green/Off and Red/Off during acquisition. (Still solid Green or Red with acquisition stopped)

List-mode support (requires FP5.13) [CLKL and SYNC commands; Request packet PIDs 3/9 and 0xF0/0x16; Response packet PIDs 0x82/0x0A and 0x82/0x0B; ACK PID 0xFF/0x10]

Fixed RTDS rounding error

#### 1.22 FW6.06.04

PX5: added support for HPGe HVPS option (HVSE and PAPS commands; Status packet)

New uC/FPGA upload packet types to improve reliability over Ethernet

Erased/uninitialized/corrupt FPGA will report FP15.15 (i.e. 0xFF)

DP5/PX5: Ethernet UDP socket is no longer closed when USB VBus is detected, i.e. when USB is connected

#### 1.23 FW6.06.03

Changed input offset default values for "INOF=DEF" to accommodate PX5 front end

DPG: Ethernet UDP socket is no longer closed when USB VBus is detected, i.e. when USB is connected

#### 1.24 FW6.06.02

Fixed SOFF command readback bug for -1 < SOFF < 0

PX5: fixed bug with PAPS command readback (read back 8.5 when set to 5)

#### 1.25 FW6.06.01

PX5: added HV polarity to status packet

#### 1.26 FW6.06.00 / FP5.11

Channel numbers were changed to start with channel 0, not channel 1, to be consistent with industry standards. This affects the following text commands: MCSL, MCSH, PRCL, PRCH, SCAL, SCAH,

Amptek Inc. Page 10 of 180

TLLD. The data format in the spectrum response packets is unchanged, but software should interpret the first channel to be channel 0, not channel 1, to be consistent with the above commands.

The fine gain now has a minimum precision of 1 part in 8192. (It was as low as 1 part in 256 in FP5.10.) This allows the 'GAIN' and 'GAIF' to be set with the precision of 1 channel or better.

Calibration of the PX5 and DP5/PC5 HV supplies is supported.

PAPZ (preamp pole-zero) command for PX5.

Fixed RTD; in FP5.09/FP5.10, only worked with TPFA (fast peaking time) of 100nS (80MHz) or 400nS (20MHz).

Added a 'build number' to the firmware version, in byte 37 of the status packet; FW6.06, build 0 is listed as FW6.06.00.

Improved precision of THFA (Fast Threshold) and THSL (Shaped Threshold) commands.

Added input offset gain command ('INOG') for PX5

#### 1.27 FW6.05 / FP5.10

RS232: A 'Gap timer' was added; support for 57.6kbaud and 19.2kbaud was added, in addition to the standard 115.2kbaud. (See section 3.3).

Added 'reboot' bit to status packet, to aid in detecting unexpected reboot/power cycle.

#### 1.28 FW6.04 / FP5.10

UDP receive buffer was expanded to handle 590-byte DHCP response

Fixed THFA readback for unconfigured condition

Fixed 'Unit is Configured' bit in status packet

#### 1.29 FW6.03 / FP5.10

CON1 & CON2 commands for GammaRad (DP5G/PC5G) and PX5

#### 1.30 FW6.02 / FP5.09

Shaped channel peaking times ('TPEA') down to 50nS; Fast channel peaking times ('TPFA') down to 50nS

UDP port inactivity timeout was increased from 5 to 15 seconds

#### 2 Software

#### 2.1 Uploading new firmware

The Firmware Manager application can be downloaded from the Amptek website for use in loading new firmware, changing various calibration settings, or changing the TCP/IP configuration of the device. Firmware Manager can be downloaded from here:

Amptek Inc. Page 11 of 180

http://www.amptek.com/firmware/firmwaremanager.zip

Firmware Manager works best if it is allowed to access the Internet, in which case it can install the very latest firmware. However, the ZIP file download includes all current firmware files, so they can be manually installed as needed.

Firmware Manager replaces the Firmware Loader and DP5 Loader applications. Firmware Manager can upgrade FW5-based DP5s via RS232, and all other devices via USB, Ethernet or RS232.

#### 2.2 Software Resources

There are a number of resources available to assist in developing an application:

#### 2.2.1 **DP5 VB Demo**

The DP5 VB Demo can be downloaded from the Amptek website. It is written in Visual Basic 5, and shows how to use WinUSB, Winsock, and the VB Comm control to communicate with a DP5-family device. It handles nearly all packet types; it can upload new firmware and set various calibration values; it supports List Mode, though not at the highest count rates.

http://www.amptek.com/zip/dppsoft\_3.zip

#### 2.2.2 SDK

A Software Development Kit (SDK) is available from the Amptek website. It has C++ and VB examples. Labview and other language examples may also be found on the website. Contact Amptek for more information.

http://www.amptek.com/products/dp5-digital-pulse-processor-software/

#### 3 Interfaces

The DP5 supports three communication interfaces: USB, Ethernet and RS232. Details about the specific interfaces are in the following sections.

Note: Attempting to use multiple interfaces simultaneously can result in unexpected behavior. In firmware prior to FW6.06.04 (DP5/PX5) or FW6.06.03 (DP5G), the Ethernet general UDP socket is disabled whenever the USB port is connected to a live host port. The socket is re-enabled if the USB cable is disconnected, or the host/hub to which the DP5 is physically connected is powered off. In FW6.06.04 (DP5/PX5) or FW6.06.03 (DP5G) and later, this is no longer the case – the UDP port is always open, regardless of whether USB is connected. [This was changed because noise on the unconnected USB connector caused Ethernet dropouts.]

The 'Netfinder' socket remains functional when USB is connected, and the contents of the Netfinder packet indicate if the UDP socket is unavailable because of USB.

The DP5G checks to see if either the USB or RS232 connectors are connected to a live port at power-up. If so, the Ethernet controller is not initialized (to save power), and will remain non-functional until the next power cycle.

Amptek Inc. Page 12 of 180

#### 3.1 USB

The DP5 family supports 'full-speed' (12Mbps) USB 2.0. Three endpoints are used: the 'control' endpoint (EP0); EP1 IN (for response packets from the DP5 to host PC); and EP2 OUT (for request packets from the host PC to DP5.)

Transfers on EP1 and EP2 are terminated by a 'short packet' (a packet smaller than the max packet size of 64 bytes), or a zero-length packet ('ZLP').

For the DP5, PX5, DP5G, and MCA8000D, the USB Vendor ID (VID) and Product ID (PID) are:

VID: 0x10C4 PID: 0x842A

The DPPMCA application (and DP5 Visual Basic demo) use the WinUSB driver. This is a Microsoft product that is native to Vista and Windows 7 (32- and 64-bit), and installable on WinXP. The Visual Basic demo includes source code, and VC++ classes are available for those wishing to write their own communication software.

#### 3.1.1 Installing the WinUSB Driver

The WinUSB driver has been tested by WinQual and signed for WinXP 32/64, Vista 32/64, and Win7 32/64. It is available via Windows Update, which means that a PC with an Internet connection should be able to install the driver automatically. Directions for manually installing the driver are in the 'WinUSB Driver Installation' folder in the ZIP file.

The ZIP file includes the Microsoft document 'WinUsb\_HowTo.docx', which describes the complex process of using Windows' SetupAPI to find the device path, etc. [The VB demo demonstrates this technique, as well as setting pipe policies, opening pipes, sending and receiving data, etc.]

USB.h and USB100.h contain many structures, enums, etc. used by Windows' USB implementation – these files (from DDK6001) are in the ZIP file.

Microsoft's website gives information on how to call the specific WinUSB functions: <a href="http://msdn.microsoft.com/en-us/library/ff540046(v=VS.85).aspx">http://msdn.microsoft.com/en-us/library/ff540046(v=VS.85).aspx</a>

As of FW6.07.04, Windows 8 USB descriptors have been added, which may allow Win8 to automatically load WinUSB without having to install it. Microsoft's documentation is a bit sketchy on this; it hasn't been tested yet at Amptek.

Win8 descriptors added:

- 1. An 'OS String Descriptor', to tell Windows that extended feature descriptors are present;

- 2. An 'Extended Compat ID OS feature descriptor', to tell Windows to use WinUSB; and

- 3. An 'Extended properties OS feature descriptor', to specify the device's interface GUID.

#### 3.1.2 WinUSB GUIDs

The WinUSB driver for the DP5 family utilizes two GUIDs:

FW6 GUIDs:

Amptek Inc. Page 13 of 180

Setup Class GUID: {6A4E9A2D-9368-4f01-8E60-B3F9CDBAB5E8} Interface Class GUID: {5A8ED6A1-7FC3-4b6a-A536-95DF35D03448}

#### 3.2 Ethernet

The DP5 incorporates a 10base-T Ethernet controller and embedded TCP/IP stack to provide Ethernet support via a standard RJ45 jack. The DP5 supports auto-negotiation for half- and full-duplex. Only 10Mbit/s is supported.

PING and ARP are supported. A fixed IP address can be specified, or a dynamic address can be obtained from a DHCP server. (If 'dynamic' is selected, and the DP5 is unsuccessful in obtaining a lease from a DHCP server, it will fall back to its previously-programmed static address.) The IP configuration (fixed/dynamic, IP address, netmask, gateway, and port) can be programmed via any of the DP5 communication interfaces (Ethernet, USB or RS232).

Note: By default, the DP5/PX5/DP5G is configured to use a dynamic IP address. If no DHCP server is present, then the device falls back to the programmed static IP address. Prior to FW6.06.05, if no static IP address was programmed, then the device defaulted to 255.255.255.255, which is not a valid IP address. In this case, if a DHCP server isn't available, then USB or RS232 must be used to assign a valid static IP address. The Firmware Manager application is the preferred way to assign an IP address, although the DP5 VB Demo can also perform this function. In FW6.06.05 and later, if no DHCP server is present and a static IP address hasn't been programmed, the device will default to 192.168.1.10.

In addition, in order to save power, the DP5G powers down the Ethernet controller when a USB or RS232 connection is detected at power-up. This means for a Gammarad (or other devices that can be powered via USB), external power should be applied, and then USB (or RS232) can be connected after approximately five seconds (or more).

Also, for whatever reason, the DP5/PX5/DP5G work poorly via Ethernet when directly connected to a PC's Ethernet port. They work fine if connected to the PC via an Ethernet hub or switch.

#### **3.2.1** Ping

Prior to FW6.06.06, the Ethernet implementation had a 32-byte PING buffer. This worked with Windows, but not with the Linux default ping size of 56 bytes. In FW6.06.06, the PING buffer was increased to accommodate the Linux default ping size. Note that for Linux ping support with older firmware, the Linux default ping size can be overridden.

#### 3.2.2 Ethernet Ports

The DP5 supports two UDP ports for communication: one port is for general communications (fixed at UDP port 10001 in FW6.06, and possibly programmable in later firmware releases), and the other is for device discovery via the Silicon Labs Netfinder protocol (UDP port 3040.)

#### 3.2.3 General UDP Port

By default, the DP5 uses UDP port 10001 for communications. Once a packet exchange has taken place on this port, the socket is 'bound' to the IP address **and source port** of the host it exchanged packets with. Once the socket is bound, packets from other IP addresses will be ignored. After approx. 15 seconds of inactivity on the socket, the socket is reset so that it can once again connect to any IP.

Amptek Inc. Page 14 of 180

To not allow other hosts to seize control of the DP5, the host can continue exchanging packets so that this timeout does not occur. "Interface keep-alive" Request Packets can be sent periodically, if there is no other periodic traffic, to keep the socket from resetting. Or an "Interface – lock" Request Packet can be sent, in which case the socket will not be reset until power is cycled on the DP5, or the host removes the lock by sending an "Interface keep-alive - allow sharing" or "Interface keep-alive - no sharing" Request Packet.

Broadcast packets can be received by the General UDP Port, which may be useful if multiple DP5s are on a subnet, and synchronization or centralized control is desired. (Request packets such as 'Enable MCA' and 'Clear Spectrum' could be useful as broadcasts.) As of firmware FW6.06, all Request Packets received by the DP5 will generate a Response Packet, which isn't desirable for broadcasts. Future versions of the firmware may use the most significant bit of the PID2 packet ID to indicate a broadcast packet, so that DP5s will be able to suppress Response Packets. Also, a command or Request Packet will be added so that a DP5 can be configured whether to process or ignore broadcast packets. (This will allow some DP5s on a subnet to not participate in broadcasts, if this is desired.)

The existing protocol works over the Internet, but possibly not very well. As it uses raw UDP packets with no sequence numbers, and spectrum packets are large enough that they're split into multiple UDP packets, theoretically the spectrum UDP packets could be received out of sequence, with no way to tell. Eventually, the firmware will have the option to encapsulate each UDP packet within the DP5 packet structure, and use the DP5 packet PIDs as sequence numbers. This should allow the protocol to be more robust when routed over the Internet – the packets will be able to be reordered if they arrive out of sequence, and it will be easier to detect dropped packets.

#### **Timeouts**

Generally, the DP5 sends the Response or ACK packet after it has completed the operation specified by the Request Packet. This is usually happens quickly, so that the response is sent with little delay. Since the DP5 always sends a Response or ACK Packet in response to receiving a Request Packet, it may be desirable to use a timeout interval to identify missed packets.

The Visual Basic demonstration software uses a timeout interval of 1000mS by default. However, there are a few packet types which require a longer timeout interval because they may take longer than 1s to execute:

| Description         | PID1 | PID2 | LEN<br>MSB | LEN<br>LSB | Recommended<br>Timeout |

|---------------------|------|------|------------|------------|------------------------|

| Request diagnostic  |      |      |            |            |                        |

| data                | 3    | 5    | 0          | 0          | 2500mS                 |

| Erase FPGA image    | 0x30 | 1    | 0          | 2          | 5000mS                 |

| Erase uC image #1   | 0x30 | 5    | 0          | 2          | 2000mS                 |

| Write 512-byte Misc |      |      |            |            |                        |

| Data                | 0xF0 | 0x09 | 2          | 0          | 1000mS                 |

#### 3.2.4 Netfinder UDP port 3040

The DP5 supports the Silicon Labs 'Netfinder' protocol on UDP port 3040. This allows DP5s to be 'discovered' – this is particularly useful if DHCP is used to assign dynamic IP addresses, as the DP5 may have an unknown address.

By broadcasting a Netfinder 'Broadcast Identity Request' to UDP port 3040, the host directs all DP5s that receive the broadcast to respond with an 'Identity Reply', which includes the DP5 serial number, IP

Amptek Inc. Page 15 of 180

address, MAC address, a text description (if one was programmed), the time the device has been powered, and the status of the interface. The host collects the responses from all the DP5s on the subnet, and can then determine which IP address to access based on DP5 serial number, description, etc.

The 'Broadcast Identity Request' is 6 bytes in size and is defined below. The format of the 'Identity Reply' is also listed below – its size is variable because it contains several variable-length null-terminated strings. Note that the 2<sup>nd</sup> string, the description, comes from the DP5's 'Misc Data' buffer. If the firmware finds a null-terminated string of 40 characters or less, it will send that as the description string. Otherwise, '(no description)' is used. [Note: the DP5 will <u>not</u> respond to the Netfinder 'standard' 4-byte version of the 'Broadcast Identity Request' as defined by Silicon Labs.]

Note that because UDP packet reception is not guaranteed (packets aren't automatically resent), occasionally not all responses will be received. It may be necessary to send multiple Identity Request packets to receive responses to all units. (This depends on how busy the network is, and how many DP5s are present.) Each subsequent Identity Request should use a different sequence ID – a DP5 will not respond to a repeated Identity Request with the same sequence ID.

Note that while the 'Broadcast Identity Request' packet is normally sent as a UDP broadcast packet (i.e. a destination IP of xxx.xxx.xxx.255), it can also be sent to a specific IP address. Also note that UDP broadcast packets generally are limited to the local subnet, and not routed beyond that.

The 'Interface Sharing Request' format is also listed below. If a Netfinder Identity Reply has indicated that a DP5 is in use, but that sharing is allowed, the host can send the 'Interface Sharing Request' to the Netfinder port of that DP5. The DP5 will use an ACK packet to indicate to its current host that a Sharing Request has been received. If that host wishes to grant the request, it does so by stopping transfers to the DP5's UDP socket, which will allow the socket to reset itself and the new host to gain control of it. [No acknowledgement of the 'Interface Sharing Request' is sent by the DP5 – the host can resend it periodically, and either check the Interface Status in the Netfinder 'Identity Reply', or try sending packets to the DP5 UDP port to see if it responds.]

Broadcast Identity Request – 6 bytes

| Offset | 0    | 1    | 2 | 3                  | 4    | 5        |

|--------|------|------|---|--------------------|------|----------|

| Value  | 0x00 | 0x00 |   | n 16-bit<br>nce ID | 0xF4 | 0x<br>FA |

Identity Reply – variable length

| Data<br>Offset                                  | Value                                                |  |

|-------------------------------------------------|------------------------------------------------------|--|

| 0                                               | 0x01                                                 |  |

| 1 Ethernet General UDP Port Status:             |                                                      |  |

|                                                 | 0 = Interface is open (unconnected);                 |  |

| 1 = Interface is connected (sharing is allowed) |                                                      |  |

|                                                 | 2 = Interface is connected (sharing is not allowed); |  |

|                                                 | 3 = Interface is locked                              |  |

Amptek Inc. Page 16 of 180

|          | 4 = Interface is unavailable because USB is connected                                                                                                                                                              |

|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2-3      | Replication of Random 16-bit sequence ID received from 'Identity Request'                                                                                                                                          |

| 4-5      | Event 1 Days                                                                                                                                                                                                       |

| 6        | Event 1 Hours                                                                                                                                                                                                      |

| 7        | Event 1 Minutes                                                                                                                                                                                                    |

| 8-9      | Event 2 Days                                                                                                                                                                                                       |

| 10       | Event 2 Hours                                                                                                                                                                                                      |

| 11       | Event 2 Minutes                                                                                                                                                                                                    |

| 12       | Event 1 Seconds                                                                                                                                                                                                    |

| 13       | Event 2 Seconds                                                                                                                                                                                                    |

| 14-19    | MAC address (MSBLSB)                                                                                                                                                                                               |

| 20-23    | IP Address (MSBLSB)                                                                                                                                                                                                |

| 24-27    | Subnet Mask (MSBLSB)                                                                                                                                                                                               |

| 28-31    | Default Gateway (MSBLSB)                                                                                                                                                                                           |

| variable | Null-terminated string:  'Amptek DP5 – S/N' + serial number  'Amptek PX5 – S/N' + serial number  'Amptek DP5G – S/N' + serial number  'Amptek TB-5 – S/N' + serial number  'Amptek MCA8000D – S/N' + serial number |

| variable | Null-terminated string – Description/misc text: "(no description)" if Misc Text isn't programmed; first 41 bytes of Misc Text if programmed                                                                        |

| variable | Null-terminated string – Event 1 description: "Time Powered"                                                                                                                                                       |

| variable | Null-terminated string – Event 2 description: "Time on Network"                                                                                                                                                    |

Interface Sharing Request – 6 bytes

| Offset | 0    | 1    | 2           | 3              | 4    | 5    |

|--------|------|------|-------------|----------------|------|------|

| Value  | 0x04 | 0x00 | Random 16-b | it sequence ID | 0xF4 | 0xFA |

## 3.3 RS232

The RS232 port on the DP5 operates at 115,200 baud, with 1 start bit, 8 data bits, no parity bit, and 1 stop bit. Neither hardware nor software handshaking is used. 57,600 or 19,200 baud operation can be selected; however, selecting these rates will disable the Ethernet port.

Amptek Inc. Page 17 of 180

The RS232 interface employs a 'gap timer' on its receiver, to aid in synchronization – if the time between consecutive received bytes exceeds 100mS, all buffered bytes are discarded, and the DP5 will resume searching for the sync characters that signal the start of a new packet. No acknowledge packet will be sent to indicate this has occurred.

#### 3.4 Transfer times and data buffering deadtime

In response to a Spectrum (or spectrum + status) request packet, the DP5 will briefly shut off data acquisition, so that it can make a copy of the spectrum memory. When complete, the MCA is re-enabled and the acquisition continues. This 'deadtime' is a function of how many channels are selected (256, 512, etc.) and whether the FPGA is running at 20 or 80MHz. This 'deadtime' will occur each time the spectrum is read out, and this is reflected in the acquisition time; the acquisition timer is stopped during this 'deadtime', while the realtime timer continues to run.

[Note that there is no deadtime penalty for using the 'request spectrum and clear' (or 'request spectrum + status and clear') form of the request packet – the clear function happens simultaneously with the buffering function, and does not add to the 'deadtime'.]

| The measured | 'deadtimes' | are: |

|--------------|-------------|------|

|              |             |      |

| # of Channels      | 20MHz Clock | 80MHz Clock |

|--------------------|-------------|-------------|

| 256                | 228uS       | 113uS       |

| 512                | 420uS       | 189uS       |

| 1024               | 804uS       | 343uS       |

| 2048               | 1.57mS      | 650uS       |

| 4096               | 3.12mS      | 1.27mS      |

| 8192               | 6.18mS      | 2.50mS      |

| Status packet only | 31uS        | 31uS        |

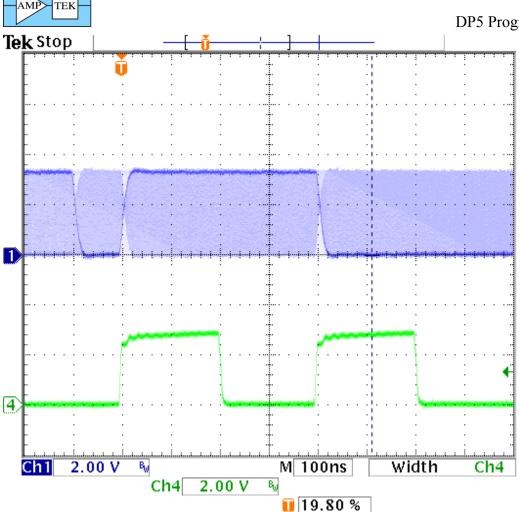

The USB, Ethernet and RS232 transfer times were measured, using an oscilloscope. The transfer times include the time from when the request packet was started to when the response packet was completed. (i.e. the whole round-trip transfer was measured.)

The transfer times include the 'deadtime' due to buffering, listed above. The transfer times were measured with the 80MHz clock selected, and were measured using the 'Request spectrum + status' request packet. The transfers will run at the same rate with the 20MHz clock, except the 'deadtime' for buffering will be longer. So, for 20MHz timing, use the 80MHz timing, plus the difference between the 20MHz and 80MHz buffering 'deadtime'.

| # of     | USB     | Ethernet (80MHz) | RS232         | RS232        |

|----------|---------|------------------|---------------|--------------|

| Channels | (80MHz) |                  | (115k, 80MHz) | (57k, 80MHz) |

| 256      | 2.8mS   | 11mS             | 74mS          | 146mS        |

Amptek Inc. Page 18 of 180

| 512  | 3.5mS  | 19mS  | 140mS | 279mS |

|------|--------|-------|-------|-------|

| 1024 | 4.8mS  | 35mS  | 273mS | 544mS |

| 2048 | 7.5mS  | 70mS  | 538mS | 1.07S |

| 4096 | 12.7mS | 134mS | 1.07S | 2.14S |

| 8192 | 24.2mS | 263mS | 2.14S | 4.22S |

Amptek Inc. Page 19 of 180

#### 4 Packet Format

All communications with the DP5 follow a request/response format: the host sends a Request Packet to the DP5, and the DP5 returns a Response Packet. The Response Packet sent by the DP5 to the host will be:

- a. a packet containing the requested data;

- b. an acknowledge (ACK) packet, indicating the request packet was received and interpreted without error (if the request packet is not one for which data is returned);

- c. an ACK packet, indicating the request packet contains an error in structure or content;

- d. an ACK packet, indicating why the request can't be executed;

- e. an ACK packet, indicating that an ASCII command had a unrecognized command field or an invalid parameter field the command in question will be echoed in the data field of the ACK packet.

- f. an ACK packet, indicating the request packet was received and interpreted without error, and a sharing request was received from another computer via Ethernet;

All packets sent to and from the DP5 use the same basic packet format: a 6-byte header, which defines the type and length of the packet, an optional data field, and a 16-bit checksum. For packets sent to the DP5, the optional data field can be up to 512 bytes, for a maximum packet size of 520 bytes. For packets sent by the DP5 to the host PC, the maximum data field size is 32767 for a maximum packet size of 32775 bytes.

#### Packet Format

| Offset | 0    | 1    | 2    | 3    | 4       | 5       | 65+LEN          | 6+LEN  | 7+LEN  |

|--------|------|------|------|------|---------|---------|-----------------|--------|--------|

|        |      |      |      |      |         |         | Data (optional, | CHKSUM | CHKSUM |

| Value  | 0xF5 | 0xFA | PID1 | PID2 | LEN_MSB | LEN_LSB | 0-512 bytes)    | MSB    | LSB    |

Fields:

Offset 0 & 1: Sync bytes – these fields have fixed values of 0xF5 and 0xFA.

Offset 2 & 3: Packet ID fields 1 & 2 (PID1 & PID2) – these define the meaning of the packet,

as summarized in Table 1, Table 2 and Table 3.

Offset 4 & 5: 16-bit length field (LEN) of the optional data field. If data field is not present,

LEN=0.

If LEN =0:

Offset 6 & 7: 16-bit checksum: MSB, then LSB. This is a two's-complement of the 16-bit sum

of all bytes prior to the checksum. (i.e. the 16-bit sum of the checksum and all

other bytes in the packet is 0.)

If LEN > 0:

Offset 6: The start of the data field, whose length is given by the 16-bit LEN field. The last

byte is offset 5+LEN.

Offset 6+LEN, Checksum, as described above.

7+LEN:

Amptek Inc. Page 20 of 180

## 4.1 Request Packets (Host PC to DP5)

Table 1 – Text highlighted in Blue is new/modified since Rev A6 of the Programmer's Guide

| Description                  | Support*  | PID1  | PID2 | LEN<br>MSB | LEN<br>LSB | Data (optional)      | Response        |

|------------------------------|-----------|-------|------|------------|------------|----------------------|-----------------|

| Request status packet        | ALL       | 1     | 1    | 0          | 0          |                      | Data packet     |

| Request spectrum             | ALL       | 2     | 1    | 0          | 0          |                      | Data packet     |

| Request & clear              |           |       |      |            |            |                      | •               |

| spectrum                     | ALL       | 2     | 2    | 0          | 0          |                      | Data packet     |

| Request spectrum +           |           |       |      |            |            |                      |                 |

| status                       | ALL       | 2     | 3    | 0          | 0          |                      | Data packet     |

| Request & clear              |           | _     |      | _          | _          |                      |                 |

| spectrum + status            | ALL       | 2     | 4    | 0          | 0          |                      | Data packet     |

| Buffer spectrum              | 6.08.00   | 2     | 5    | 0          | 2          | Buffer # (MSB first) | ACK packet      |

| Buffer & clear spectrum      | 6.08.00   | 2     | 6    | 0          | 2          | Buffer # (MSB first) | ACK packet      |

| Request buffer               | 6.08.00   | 2     | 7    | 0          | 2          | Buffer # (MSB first) | Data packet     |

| Request digital scope        |           |       |      |            |            |                      |                 |

| data                         | ALL       | 3     | 1    | 0          | 0          |                      | Data packet     |

| Request 512-byte misc        |           |       |      |            |            |                      |                 |

| data                         | ALL       | 3     | 2    | 0          | 0          |                      | Data packet     |

| Request digital scope        |           | 0     |      | 0          |            |                      | Data madest     |

| data & re-arm scope          | ALL       | 3     | 3    | 0          | 0          |                      | Data packet     |

| Request Ethernet settings    | ALL       | 3     | 4    | 0          | 0          |                      | Data packet     |

| Request diagnostic           | ALL       |       | 4    | U          | 0          |                      | Вата раскет     |

| data                         | ALL       | 3     | 5    | 0          | 0          |                      | Data packet     |

| Request Netfinder            | , , , , , |       |      |            |            |                      | Data paonot     |

| packet                       | 6.01      | 3     | 7    | 0          | 0          |                      | Data packet     |

| •                            |           |       |      |            | u          | I2C transfer         | '               |

| Perform I2C transfer         | 6.01      | 3     | 8    | vari       | es         | description          | ACK or Data     |

| Request List-mode data       | 6.06.05   | 3     | 9    | 0          | 0          |                      | ACK or Data     |

| Request Option PA            | 6.07.02;  |       |      |            |            |                      |                 |

| calibration data             | M         | 3     | 0x0A | 0          | 0          |                      | ACK or Data     |

| Request 32-bit SCA           |           |       |      | _          | _          |                      |                 |

| counters                     | ALL       | 4     | 1    | 0          | 0          |                      | Data packet     |

| Latch + Request 32-bit       | A. I.     | 4     |      | 0          |            |                      | Doto pookot     |

| SCA counters Latch + Clear + | ALL       | 4     | 2    | 0          | 0          |                      | Data packet     |

| Request 32-bit SCA           |           |       |      |            |            |                      |                 |

| counters                     | ALL       | 4     | 3    | 0          | 0          |                      | Data packet     |

| Text configuration (to       | ALL       |       |      | 0          |            | ASCII                | Data packet     |

| DP5)                         | ALL       | 0x20  | 2    | vari       | es         | configuration        | ACK packet      |

| Text configuration           | , ,==     | 07120 |      |            |            | ASCII                | , to the parent |

| Readback (from DP5)          | 6.01      | 0x20  | 3    | vari       | es         | configuration        | Data packet     |

| Text configuration (to       |           |       |      |            |            |                      | •               |

| DP5) without saving to       | 6.08.00;  |       |      |            |            | ASCII                |                 |

| nonvolatile memory           | ALL       | 0x20  | 4    | vari       |            | configuration        | ACK packet      |

| Erase FPGA image             | ALL       | 0x30  | 1    | 0          | 2          | 0x12 0x34            | ACK packet      |

| Upload packet (FPGA)         | ALL       | 0x30  | 2    | vari       | es         |                      | ACK packet      |

| Reinitialize FPGA            | 6.06.01   | 0x30  | 3    | 0          | 0          |                      |                 |

| Erase uC image #1            | ALL       | 0x30  | 5    | 0          | 2          | 0x12 0x34            | ACK packet      |

| Upload packet (uC)           | ALL       | 0x30  | 7    | vari       |            |                      | ACK packet      |

| Switch to uC image #1        | ALL       | 0x30  | 9    | 0          | 4          | 0xA5 0xF1 CS         | ACK packet      |

Amptek Inc. Page 21 of 180

|                                      |                     | 1        |      |     | 1                                                | MSB, LSB           |                       |

|--------------------------------------|---------------------|----------|------|-----|--------------------------------------------------|--------------------|-----------------------|

| Upload packet (FPGA),                |                     |          |      |     |                                                  |                    | FPGA ACK              |

| FPGA ACK                             | 6.06.04             | 0x30     | 0x0B | var | ies                                              |                    | packet                |

| Clear Spectrum Buffer                | ALL                 | 0xF0     | 0x01 | 0   | 0                                                |                    | ACK packet            |

| Enable MCA/MCS                       | ALL                 | 0xF0     | 0x02 | 0   | 0                                                |                    | ACK packet            |

| Disable MCA/MCS                      | ALL                 | 0xF0     | 0x03 | 0   | 0                                                |                    | ACK packet            |

| Arm digital oscilloscope             | ALL                 | 0xF0     | 0x04 | 0   | 0                                                |                    | ACK packet            |

|                                      | ALL; D,             |          |      |     |                                                  |                    |                       |

| Autoset input offset                 | Р                   | 0xF0     | 0x05 | 0   | 0                                                |                    | ACK packet            |

| Autoset fast threshold               | ALL                 | 0xF0     | 0x06 | 0   | 0                                                |                    | ACK packet            |

| Read IO3-0                           |                     | 0xF0     | 0x07 | 0   | 0                                                |                    |                       |

| Write IO3-0                          | ALL                 | 0xF0     | 0x08 | 0   | 1                                                |                    | ACK packet            |

| Write 512-byte Misc                  |                     |          |      |     |                                                  |                    |                       |

| Data                                 | ALL                 | 0xF0     | 0x09 | 2   | 0                                                |                    | ACK packet            |

| 0-4-0044                             | ALL; D,             | 0 50     | 0.04 | 0   |                                                  | LOD MOD            | A O14 1 1             |

| Set DCAL                             | P                   | 0xF0     | 0x0A | 0   | 2                                                | LSB, MSB           | ACK packet            |

| Set PZ correction                    | ALL                 | 0xF0     | 0x0B | 0   | 1                                                | PZ correction      | ACK packet            |

| Set uC temp cal                      | ALL                 | 0xF0     | 0x0C | 0   | 1                                                | uC temp offset     | ACK packet            |

| Set ADC Cal                          | ALL                 | 0xF0     | 0x0E | 0   | 2                                                | gain, offset       | ACK pooket            |

| (gain/offset) Clear G.P. Counter     | ALL                 | 0xF0     | 0x0E | 0   | 0                                                | gain, onset        | ACK packet ACK packet |

| Clear G.P. Counter                   | ALL                 | UXFU     | UXIU | U   | 0                                                | Fixed/Dyn, IP[4],  | ACK packet            |

|                                      |                     |          |      |     |                                                  | Mask[4],           |                       |

|                                      |                     |          |      |     |                                                  | Gateway[4],        |                       |

|                                      |                     |          |      |     |                                                  | Dest. IP[4],       |                       |

| Set Ethernet settings                | ALL                 | 0xF0     | 0x11 | 0   | 0x13                                             | Port[2]            | ACK packet            |

| Select high-pass time                |                     |          |      |     |                                                  |                    |                       |

| constant                             | 6.01                | 0xF0     | 0x12 | 0   | 1                                                | Time constant      | ACK packet            |

| Select RS232 baud rate               | 6.05                | 0xF0     | 0x13 | 0   | 1                                                | Baud rate          | ACK packet            |

|                                      | 6.05; D,            |          |      |     |                                                  |                    |                       |

| Set HV Cal (gain/offset)             | Р                   | 0xF0     | 0x14 | 0   | 2                                                | gain, offset       | ACK packet            |

| Set 1.6uS PZ correction              | 6.06; P             | 0xF0     | 0x15 | 0   | 1                                                | PZ correction      | ACK packet            |

| Clear/Sync List-mode timer           | 6.06.05             | ٥٧٥٥     | 0,46 | 0   |                                                  |                    | ACK pookst            |

| Set zero offset, 1V                  | 6.06.05<br>6.06.07; | 0xF0     | 0x16 | 0   | 0                                                |                    | ACK packet            |

| scale                                | M.00.07,            | 0xF0     | 0x19 | 0   | 2                                                | Signed, MSB first  | ACK packet            |

| Set zero offset, 10V                 | 6.06.07;            | OXI O    | OXIO |     |                                                  | Olgrica, WOD 1113t | 7 tort paonot         |

| scale                                | M                   | 0xF0     | 0x1A | 0   | 2                                                | Signed, MSB first  | ACK packet            |

| Restart sequential                   |                     |          |      |     |                                                  | ,                  |                       |

| buffering                            | 6.08.00             | 0xF0     | 0x1E | 0   | 0                                                |                    | ACK packet            |

| Cancel sequential                    |                     |          |      |     |                                                  |                    |                       |

| buffering                            | 6.08.00             | 0xF0     | 0x1F | 0   | 0                                                |                    | ACK packet            |

| Interface keep-alive -               |                     | 0 50     | 0.00 | 0   |                                                  |                    | A O14 1 1             |

| allow sharing Interface keep-alive - | ALL                 | 0xF0     | 0x20 | 0   | 0                                                |                    | ACK packet            |

| no sharing                           | ALL                 | 0xF0     | 0x21 | 0   | 0                                                |                    | ACK packet            |

| Interface keep-alive -               | \                   | UXFU     | UAZI | U   | 0                                                |                    | AUN PAUNEL            |

| lock                                 | ALL                 | 0xF0     | 0x22 | 0   | 0                                                |                    | ACK packet            |

| Latch SCAs                           | ,                   | 07.11 0  | UNLL |     | <del>                                     </del> |                    | 7 to 1 paonot         |

| Latch + clear SCAs                   |                     |          |      |     |                                                  |                    |                       |

| Clear SCAs                           |                     | <u> </u> |      |     |                                                  |                    |                       |

|                                      | 1                   | 1        |      |     | 1                                                | 1                  | I                     |

| Comm test - Request                  |                     |          |      |     |                                                  |                    |                       |

Amptek Inc. Page 22 of 180

## DP5 Programmer's Guide Rev B0

| Comm test - Echo<br>packet      | ALL     | 0xF1 | 0x7F | vari | es     | Data to be echoed                                                     | Data packet |

|---------------------------------|---------|------|------|------|--------|-----------------------------------------------------------------------|-------------|

| Comm test - Streaming test mode | 6.07.04 | 0xF1 | 0x7E | 0    | 0 or 8 | MINA MSB, LSB;<br>MAXA MSB, LSB;<br>INCR MSB, LSB;<br>PERIOD MSB, LSB | ACK packet  |

Items in italics are considered calibration values and don't normally need to be

If not support by all three DPP types, then:

D = supported by DP5,

P = supported by PX5, and

G = supported by DP5G

Amptek Inc. Page 23 of 180

<sup>\*</sup> Initial firmware release which supports this packet type;

## 4.1.1 Request packet: "Request Status Packet"

|        | SYNC1 | SYNC2 | PID1 | PID2 | LEN<br>MSB | LEN<br>LSB | CHKSUM<br>MSB | CHKSUM<br>LSB |

|--------|-------|-------|------|------|------------|------------|---------------|---------------|

| Offset | 0     | 1     | 2    | 3    | 4          | 5          | 6             | 7             |

| Value  | 0xF5  | 0xFA  | 1    | 1    | 0          | 0          | 0xFE          | 0x0F          |

Purpose: This request directs the DP5 to construct a status packet and send it to the host PC. The status packet can be requested with this request packet, or with one of the 'Request Spectrum plus Status' variants, in which case the status packet is included in the packet data field along with the spectrum data.

The status packet contains information about the current state of the spectrum, and of the DP5. Its format is listed with the "Status Packet" Response Packet.

Response: If no errors are detected, a "Status Packet" Response Packet will be returned.

Possible errors: If the request packet is malformed or corrupted: CHKSUM, LEN, or PID error ACK packets can be returned instead of the requested data.

Amptek Inc. Page 24 of 180

## **4.1.2** Spectrum Request Packets

| Request packet: | "Request  | Specti | rum"  |

|-----------------|-----------|--------|-------|

| 2,412,          | 0) (1) 00 | DID 4  | D.D.O |

| Offset | SYNC1 | SYNC2 | PID1 | PID2 | MSB<br>4 | LSB | CHKSUM<br>MSB | LSB<br>7 |

|--------|-------|-------|------|------|----------|-----|---------------|----------|

| Value  | 0xF5  | 0xFA  | 2    | 1    | 0        | 0   | 0xFE          | 0x0E     |

Request packet: "Request and clear Spectrum"

|        |       | 0xFA  | 2    | 2    | 0          | 0          | 0xFE          | 0x0D          |

|--------|-------|-------|------|------|------------|------------|---------------|---------------|

| Offset | 0     | 1     | 2    | 2    | 1          | -5         | 6             | 7             |

|        | SYNC1 | SYNC2 | PID1 | PID2 | LEN<br>MSB | LEN<br>LSB | CHKSUM<br>MSB | CHKSUM<br>LSB |

Request packet: "Request Spectrum plus Status"